# 产品规格书

Product specifications

型号 QMDS160160V02AKW

model

## 修订记录

| 编号 | 修订内容  | 日期 | 版本   |

|----|-------|----|------|

| 1  | 新文件生成 |    | V. 1 |

|    |  |    |  |

|----|--|----|--|

| 修订 |  | 审核 |  |

| 日期 |  | 日期 |  |

## 目录

contents

| 编号 | 内容       | 页 |

|----|----------|---|

| 1  | 基本参数     |   |

| 2  | 结构尺寸图纸   |   |

| 3  | 原理图      |   |

| 4  | 极限参数值    |   |

| 5  | 光电特性     |   |

| 6  | 接口定义及说明  |   |

| 7  | MPU 指令说明 |   |

| 8  | 程序设计     |   |

| 9  | 产品使用说明   |   |

| 10 | 附件一      |   |

**1. 基本参数**

| 类型           | 规格                               | 说明          |

|--------------|----------------------------------|-------------|

| 主要硬件         | LCD 液晶屏+LED 背光+铁框+PCB 驱动电路 (SMT) |             |

| 显示模式         | FSTN 正向显示, 白底色黑字                 |             |

| 显示类型         | 半透型 LCD+白色背光                     |             |

| 物理分辨率        | 160×160                          |             |

| 外形尺寸 (mm)    | 84.0×84.0×8.50                   |             |

| 可视区尺寸 (mm)   | 62.30×62.40                      |             |

| DOT 点尺寸 (mm) | 0.335×0.335                      |             |

| DOT 点间距 (mm) | 0.35×0.35                        |             |

| 视角           | 6 O'clock                        | 12O'clock可选 |

| 占空比 (Duty)   | 1/160                            |             |

| 偏压比 (Bias)   | 1/10                             |             |

| 控制器          | UC1698U                          |             |

| 接口类型         | 8位并口, 串口, 插接                     |             |

| 模块电压         | 3.3V/5.0V                        |             |

| 工作温度 (°C)    | -20~+70                          |             |

| 存储温度 (°C)    | -30~+80                          |             |

**2. 结构尺寸图纸****2-1 产品实物图片**

图 1. 实物图片

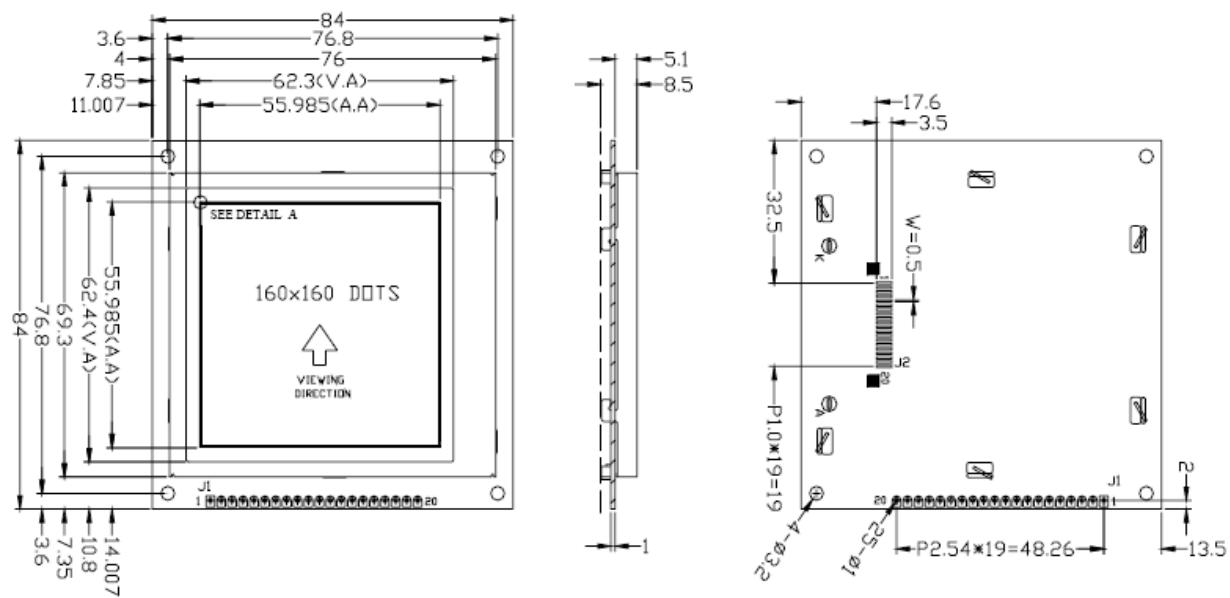

## 2-2 结构尺寸图纸内容

图 2. 产品结构图纸

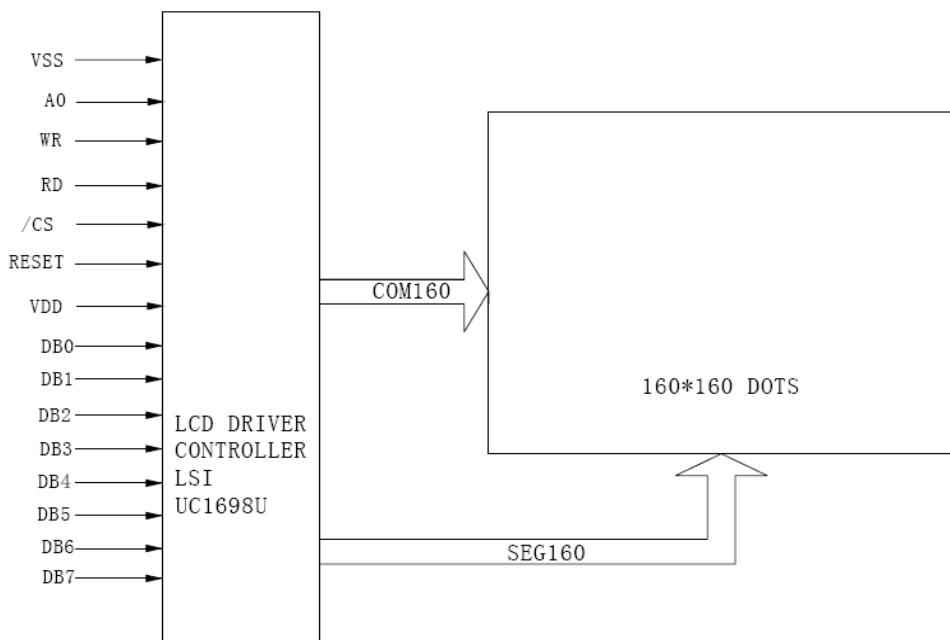

## 3. 原理图

图 3. 显示原理图

## 4. 极限参数值

### 4-1 极限电压参数

| Item      | Symbol  | Min  | Max  | Unit | Note |

|-----------|---------|------|------|------|------|

| 电源电压      | Vdd-Vss | -0.3 | 5.0  | V    |      |

| LCD 驱动电压  | Vdd-Vee | 8.0  | 18.0 | V    |      |

| I/O 口输入电压 | -       | Vss  | Vdd  | -    |      |

### 4-2 极限环境参数

| Item | Min | Max | Unit | Note |

|------|-----|-----|------|------|

| 工作温度 | -20 | 70  | °C   |      |

| 存储温度 | -30 | 80  | °C   |      |

| 环境湿度 | -   | 90  | %RH  |      |

## 5. 光电特性

### 5-1 模组电特性参数

| Item     | Symbol | Condition | Min | Typ  | Max | Unit | Note |

|----------|--------|-----------|-----|------|-----|------|------|

| 逻辑电压     | Vdd    | ----      | 2.7 | 3.3  | 5.0 | V    |      |

| LCD 驱动电压 | Vdd-Vo | ----      | 16  | 16.5 | 17  | V    |      |

| 输入电压     | VIH    | ----      | 2.0 | ---  | Vdd | V    |      |

|          | VIL    | ----      | Vss | ---  | 0.8 | V    |      |

| 频率       | FELM   | Vdd=5V    | 65  | 78   | 85  | Hz   |      |

### 5-2 背光电特性参数

| Item | Symbol | Min | Typ | Max | Unit | Condition | Note |

|------|--------|-----|-----|-----|------|-----------|------|

| 正向电压 | Vf     | 2.8 | 3.0 | 3.2 | V    | If=70mA   |      |

### 5-3 光特性参数 (测试环境25°C)

| Item                | Symbol | Condition | Min | Typ | Max | Unit | Note |

|---------------------|--------|-----------|-----|-----|-----|------|------|

| Viewing angle       | θ      | K≥2.0 φ   | 40  | --- | --- | deg  |      |

| Contrast ration     | K      | θ=50 φ    | --- | 5   | --- | ---  |      |

| Response            | Tr     | θ=50 φ    | --- | 100 | 120 | ms   |      |

| Response time(fall) | Tf     | θ=50 φ    | --- | 60  | 80  | ms   |      |

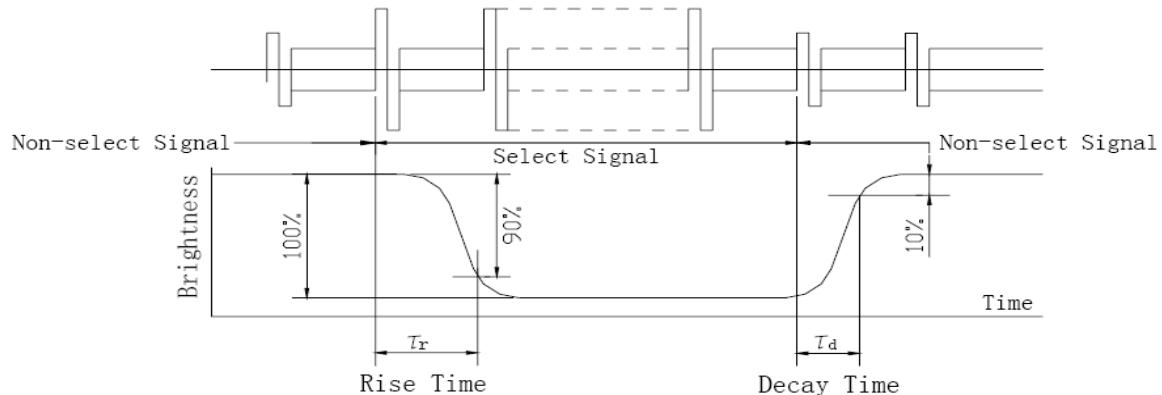

## 5-4 光学特性测定方法

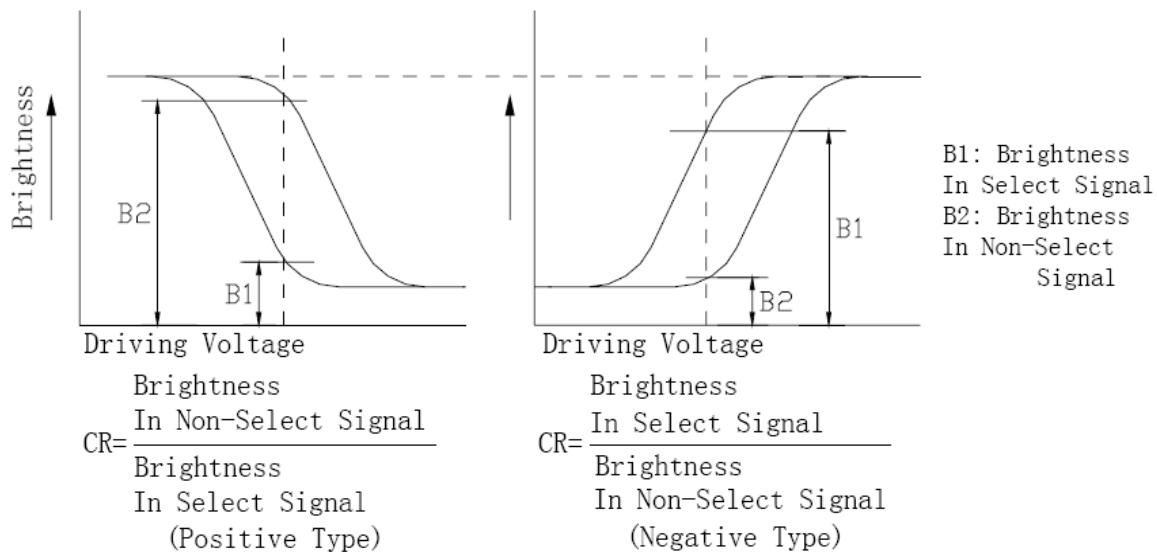

## ● Definition of Optical Response Time

In case of Negative type,

wave from of changing brightness becomes reverse

(Non Select Signals:0%, Select Signals:100%)

## ● Definition of Contrast Ratio (CR)

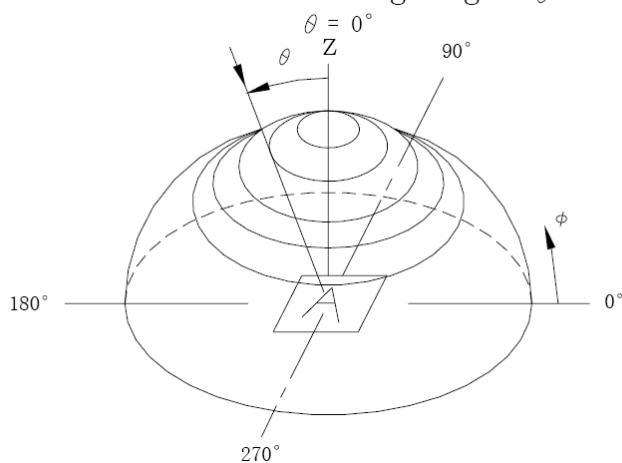

● Definition of Viewing Angle  $\theta$  and  $\phi$

## 6. 接口定义及说明

### 6-1 数据接口

| Pin | Symbol | Level | Function                                         | Note |

|-----|--------|-------|--------------------------------------------------|------|

| 1   | FG     | ----- | 铁壳地                                              |      |

| 2   | VDD    | 3.3V  | 逻辑电源正                                            |      |

| 3   | VSS    | 0V    | 逻辑电源地                                            |      |

| 4   | P/S    | H/L   | 0:并口.1:串口,                                       |      |

| 5   | C86    | H/L   | 1:6800/8BIT;0:8080/8BIT; 串口时:1:三线串口 S9,0:四线串口 S8 |      |

| 6   | /CS    | L     | LCD 选通信号, 低有效                                    |      |

| 7   | CD     | H/L   | 命令数据选择端, 高电平: 数据, 低电平: 命令                        |      |

| 8   | WR1    | H/L   | 80 时序时作为读信号, 68 时序时作为使能信号, 下降沿锁存; 串行方式时接 VSS。    |      |

| 9   | WR0    | H/L   | 80 时序时作为写信号; 68 时序时是读或写信号选择端, 串行方式接 VSS          |      |

| 10  | /RST   | L     | 复位信号, 低有效                                        |      |

| 11  | DB0    | H/L   | 数据信号线 0                                          |      |

| 12  | DB1    | H/L   | 数据信号线 1                                          |      |

| 13  | DB2    | H/L   | 数据信号线 2                                          |      |

| 14  | DB3    | H/L   | 数据信号线 3                                          |      |

| 15  | DB4    | H/L   | 数据信号线 4                                          |      |

| 16  | DB5    | H/L   | 数据信号线 5                                          |      |

| 17  | DB6    | H/L   | 数据信号线 6                                          |      |

| 18  | DB7    | H/L   | 数据信号线 7                                          |      |

| 19  | LED+   | 3.3V  | 背光电源正端                                           |      |

| 20  | LED-   | 0V    | 背光电源负端                                           |      |

| PIN | 8080/8位 | 6800/8位 | 四线串口 | 三线串口 |

|-----|---------|---------|------|------|

| P/S | 0       | 0       | 1    | 1    |

| C86 | 0       | 1       | 0    | 1    |

| /CS | /CS     | /CS     | /CS  | /CS  |

| CD  | CD      | RS      | CD   | 0    |

| WR1 | RD      | E       | 0    | 0    |

| WR0 | WR      | R/W     | 0    | 0    |

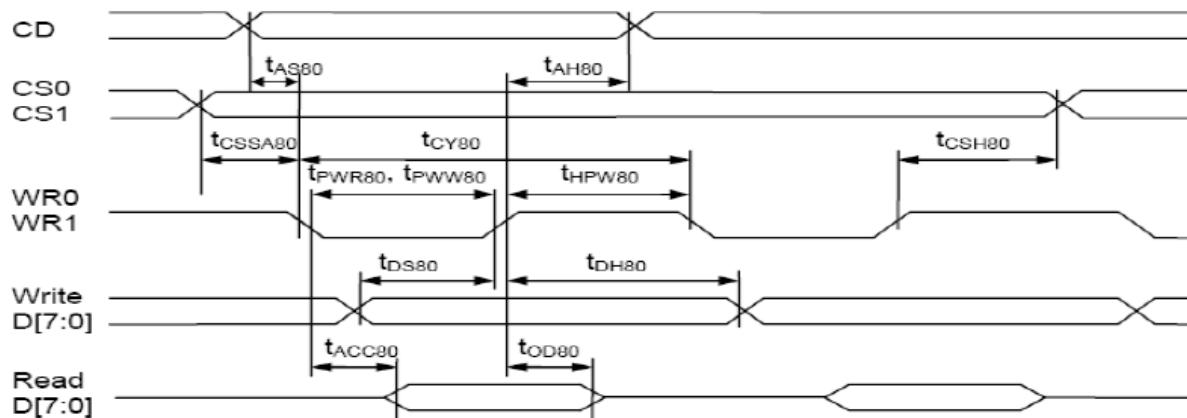

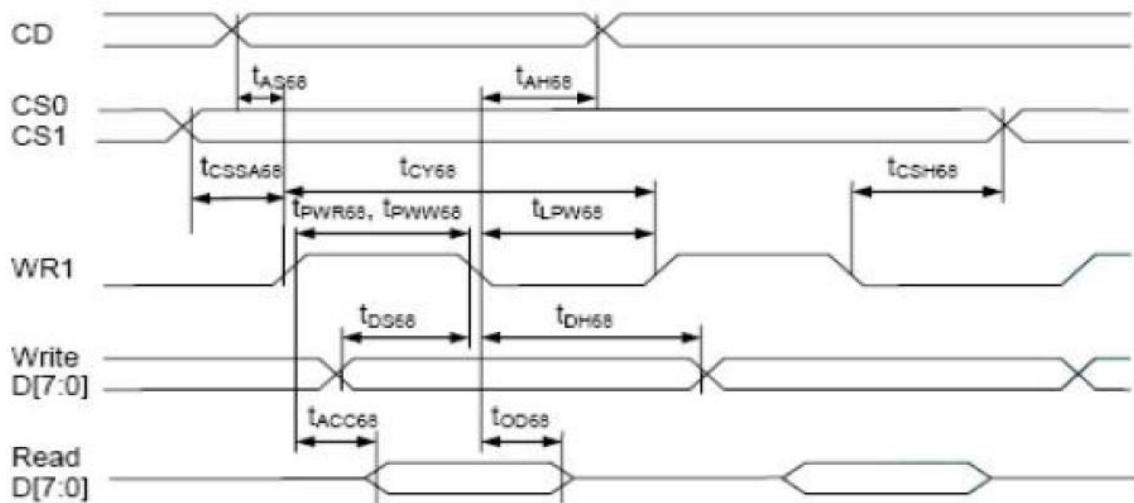

## 6-2 时序图

## 6-2-1MPU 读/写时序(8080 时序)

## 6-2-2MPU读/写时序(6800时序)

## 6-2-3MPU 时序表

| ITEM                    | SYMBOL                   | CONDITION                     | MIN. | MAX. | UNIT |

|-------------------------|--------------------------|-------------------------------|------|------|------|

| C/D SET UP TIME         | $t_{CDS}$                | VDD=3.3V<br>VSS=0V<br>TA=25°C | 0    |      | ns   |

| C/D HOLD TIME           | $t_{CDH}$                |                               | 0    |      |      |

| C/D, RD, WR PULSE WIDTH | $t_{CE}, t_{RD}, t_{WR}$ |                               | 50   |      |      |

| DATA SET UP TIME        | $t_{DS}$                 |                               | 30   |      |      |

| DATA HOLD TIME          | $t_{DH}$                 |                               | 0    |      |      |

| ACCESS TIME             | $t_{ACC}$                |                               | -    | 60   |      |

| OUTPUT HOLD TIME        | $t_{OH}$                 |                               | 15   | 30   |      |

## 7. MPU 指令说明

## 7-1 Display control instruction

UC1698u contains registers which control the chip operation. The following table is a summary of these control registers, a brief description and the default values. These registers can be modified by commands, which will be described in the next two sections, starting with a summary table, followed by a detailed instruction-by-instruction description.

Name: The Symbolic reference of the register.

Note that some symbol name refers to bits (flags) within another register.

**Default:** Numbers shown in **Bold** font are default values after Power-Up-Reset and System-Reset.

| Name                                                | Bits                                       | Default        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

|-----------------------------------------------------|--------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-----------------|-----------------|------------------------------------------------|-----------------------------------------------------|-----------------|-----------------|----------------|-------------|----------------------|-----------------------|-----------------------|-----------------------|----------------------|-----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-------------|--------------------------------------------|

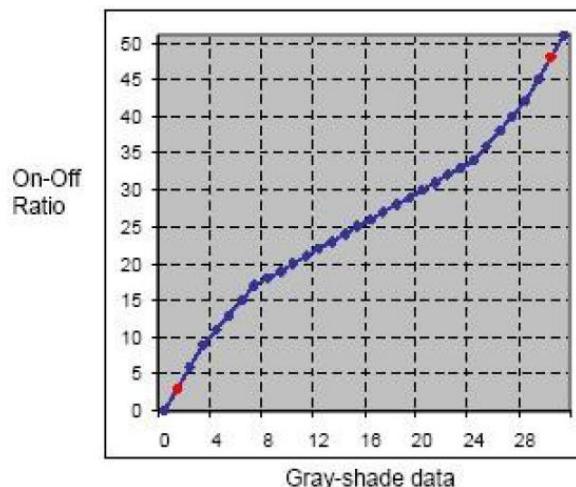

| DC                                                  | 5                                          | 18H            | <p>Display Control:</p> <p>DC[0]: PXV: Pixels Inverse. Bit-wise data Inversion. (Default 0: OFF)</p> <p>DC[1]: APO: All Pixels ON (Default 0: OFF)</p> <p>DC[2]: Display ON/OFF (Default 0: OFF)</p> <p>DC[3]: Gray-shade Modulation mode.</p> <p>0 : On/Off mode</p> <p>1 : 32-shade Mode</p> <p>DC[4]: Green Enhance Mode. Only valid in 4K-color mode.</p> <p>0 : Enable. Allows an extra display bit for green color.</p> <p>1 : Disable</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

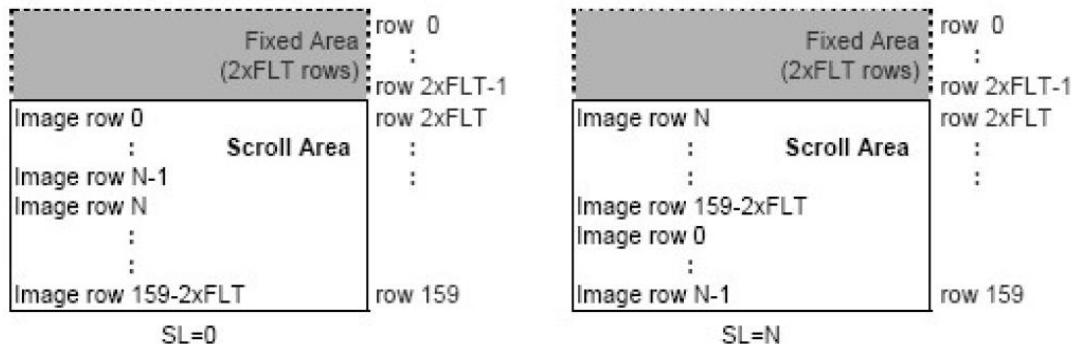

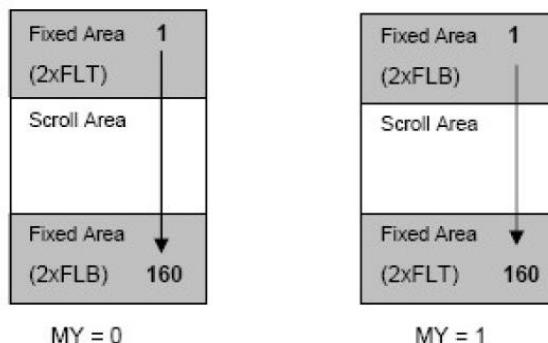

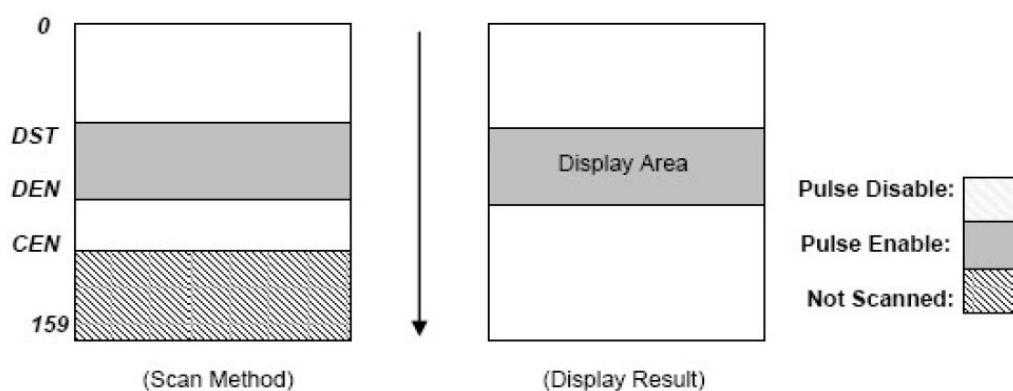

| LC                                                  | 9                                          | 090H           | <p>LCD Control:</p> <p>LC[0]: Enable the top FLT<sub>x</sub>2 and bottom FLB<sub>x</sub>2 lines in partial display mode (Default 0: OFF).</p> <p>LC[1]: MX, Mirror X. SEG/Column sequence Inversion (Default: 0: OFF)</p> <p>LC[2]: MY, Mirror Y. COM/Row sequence Inversion (Default: 0: OFF)</p> <p>LC[4:3]: Line Rate (Klips: Kilo-Line-per-second)</p> <table> <tr> <td>00b: 25.2. Klips</td> <td>01b: 30.5 Klips</td> </tr> <tr> <td>10b: 37.0 Klips</td> <td>11b: 44.8 Klips</td> </tr> </table> <p>Line Rate (for On/Off mode)</p> <table> <tr> <td>00b: 8.5 Klips</td> <td>01b: 10.4 Klips</td> </tr> <tr> <td>10b: 12.6 Klips</td> <td>11b: 15.2 Klips</td> </tr> </table> <p>(Line-Rate = Frame-Rate x Mux-Rate)</p> <p>LC[5]: RGB filter order (as mapped to SEG1, SEG2, SEG3)</p> <table> <tr> <td>0 : BGR-BGR</td> <td>1 : RGB-RGB</td> </tr> </table> <p>LC[7:6]: Color and Input mode</p> <p>when DC[4]=1:</p> <table> <tr> <td>01b : 4K color mode.</td> <td>4R-4G-4B (12-bit/RGB)</td> </tr> <tr> <td>10b : 64K color mode.</td> <td>5R-6G-5B (16-bit/RGB)</td> </tr> </table> <p>when DC[4]=0:</p> <table> <tr> <td>01b : 4K color mode.</td> <td>4R-5G-3B (12-bit/RGB)</td> </tr> <tr> <td>10b : 64K color mode.</td> <td>5R-6G-5B (16-bit/RGB)</td> </tr> </table> <p>LC[8]: Partial Display Control</p> <table> <tr> <td>0b: Disable</td> <td>Mux-Rate = CEN+1 (DST, DEN not used)</td> </tr> <tr> <td>1b: Enabled</td> <td>Mux-Rate = DEN-DST+1+LC[0] x (FLT+FLB) x 2</td> </tr> </table> | 00b: 25.2. Klips              | 01b: 30.5 Klips               | 10b: 37.0 Klips | 11b: 44.8 Klips | 00b: 8.5 Klips                                 | 01b: 10.4 Klips                                     | 10b: 12.6 Klips | 11b: 15.2 Klips | 0 : BGR-BGR    | 1 : RGB-RGB | 01b : 4K color mode. | 4R-4G-4B (12-bit/RGB) | 10b : 64K color mode. | 5R-6G-5B (16-bit/RGB) | 01b : 4K color mode. | 4R-5G-3B (12-bit/RGB) | 10b : 64K color mode. | 5R-6G-5B (16-bit/RGB) | 0b: Disable | Mux-Rate = CEN+1 (DST, DEN not used) | 1b: Enabled | Mux-Rate = DEN-DST+1+LC[0] x (FLT+FLB) x 2 |

| 00b: 25.2. Klips                                    | 01b: 30.5 Klips                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 10b: 37.0 Klips                                     | 11b: 44.8 Klips                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 00b: 8.5 Klips                                      | 01b: 10.4 Klips                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 10b: 12.6 Klips                                     | 11b: 15.2 Klips                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 0 : BGR-BGR                                         | 1 : RGB-RGB                                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 01b : 4K color mode.                                | 4R-4G-4B (12-bit/RGB)                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 10b : 64K color mode.                               | 5R-6G-5B (16-bit/RGB)                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 01b : 4K color mode.                                | 4R-5G-3B (12-bit/RGB)                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 10b : 64K color mode.                               | 5R-6G-5B (16-bit/RGB)                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 0b: Disable                                         | Mux-Rate = CEN+1 (DST, DEN not used)       |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 1b: Enabled                                         | Mux-Rate = DEN-DST+1+LC[0] x (FLT+FLB) x 2 |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

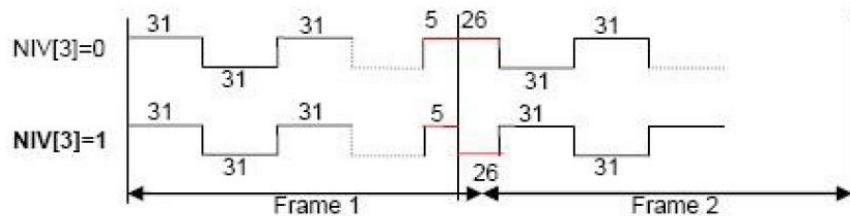

| NIV                                                 | 5                                          | 1DH            | <p>N-Line Inversion:</p> <table> <tr> <td>NIV[2:0]:</td> <td>000b: 11 lines</td> <td>001b: 19 lines</td> </tr> <tr> <td></td> <td>010b: 21 lines</td> <td>011b: 25 lines</td> </tr> <tr> <td></td> <td>100b: 29 lines</td> <td>101b: 31 lines</td> </tr> <tr> <td></td> <td>110b: 37 lines</td> <td>111b: 43 lines</td> </tr> </table> <p>NIV[3]: 0b: no-XOR</p> <p>NIV[4]: 0b: Disable NIV</p> <p>1b: XOR</p> <p>1b: Enable NIV</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NIV[2:0]:                     | 000b: 11 lines                | 001b: 19 lines  |                 | 010b: 21 lines                                 | 011b: 25 lines                                      |                 | 100b: 29 lines  | 101b: 31 lines |             | 110b: 37 lines       | 111b: 43 lines        |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| NIV[2:0]:                                           | 000b: 11 lines                             | 001b: 19 lines |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

|                                                     | 010b: 21 lines                             | 011b: 25 lines |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

|                                                     | 100b: 29 lines                             | 101b: 31 lines |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

|                                                     | 110b: 37 lines                             | 111b: 43 lines |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| CSF                                                 | 3                                          | 0H             | <p>COM Scan Function</p> <p>CSF[0]: Interlace Scan Function</p> <table> <tr> <td>0b: LRM sequence: AEBCD-AEBCD</td> </tr> <tr> <td>1b: LRM sequence: AEBCD-EBCDA</td> </tr> </table> <p>CSF[1]: FRC function</p> <table> <tr> <td>0: Disable FRC</td> </tr> <tr> <td>1: Enable FRC</td> </tr> </table> <p>CSF[2]: Shade-1 / Shade-30 option</p> <table> <tr> <td>0: Dither directly on input data (SRAM Change)</td> </tr> <tr> <td>1: PWM (Pulse-width modulation) on SEG output stage</td> </tr> </table>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0b: LRM sequence: AEBCD-AEBCD | 1b: LRM sequence: AEBCD-EBCDA | 0: Disable FRC  | 1: Enable FRC   | 0: Dither directly on input data (SRAM Change) | 1: PWM (Pulse-width modulation) on SEG output stage |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 0b: LRM sequence: AEBCD-AEBCD                       |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 1b: LRM sequence: AEBCD-EBCDA                       |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 0: Disable FRC                                      |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 1: Enable FRC                                       |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 0: Dither directly on input data (SRAM Change)      |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| 1: PWM (Pulse-width modulation) on SEG output stage |                                            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                 |                 |                                                |                                                     |                 |                 |                |             |                      |                       |                       |                       |                      |                       |                       |                       |             |                                      |             |                                            |

| Name             | Bits | Default | Description                                                                                                                                                                                                                                                            |

|------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CEN              | 8    | 9FH     | COM scanning end (last COM with full line cycle, 0 based index)                                                                                                                                                                                                        |

| DST              | 8    | 00H     | Display start (first COM with active scan pulse, 0 based index)                                                                                                                                                                                                        |

| DEN              | 8    | 9FH     | Display end (last COM with active scan pulse, 0 based index)<br>Please maintain the following relationship:<br>CEN = the actual number of pixel rows on the LCD - 1<br>CEN ≥ DEN ≥ DST+ 9                                                                              |

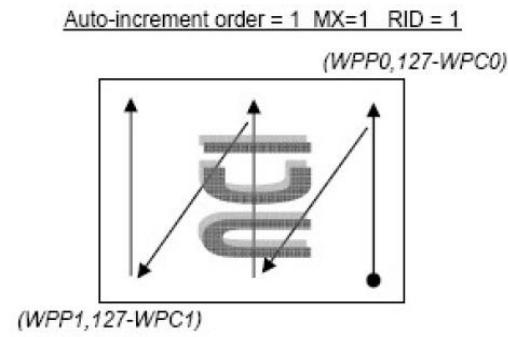

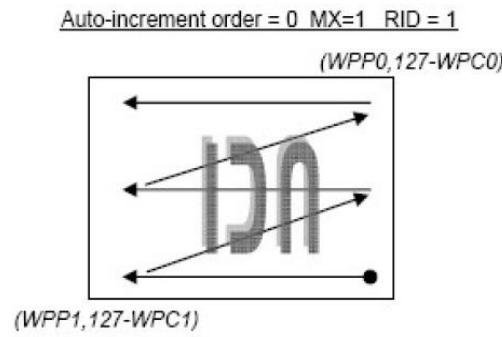

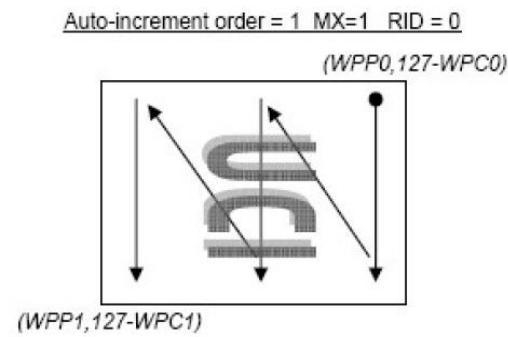

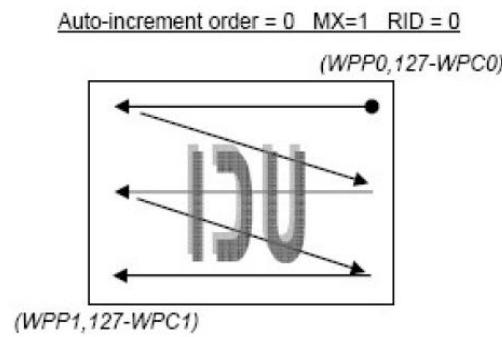

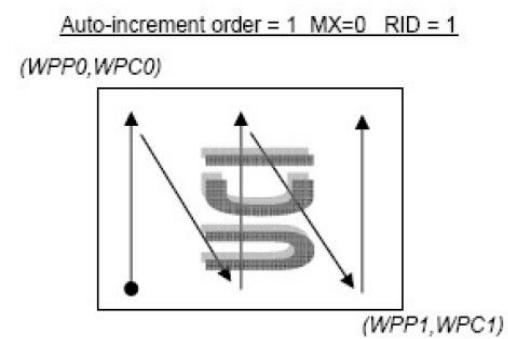

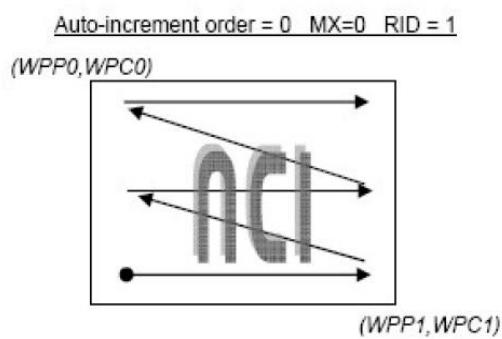

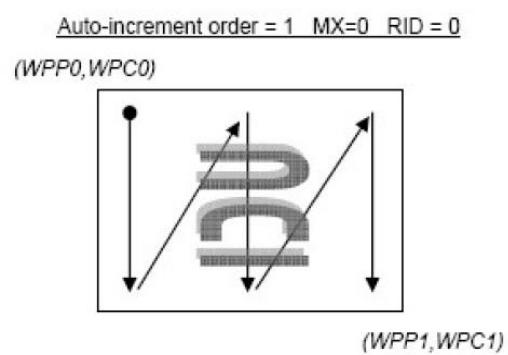

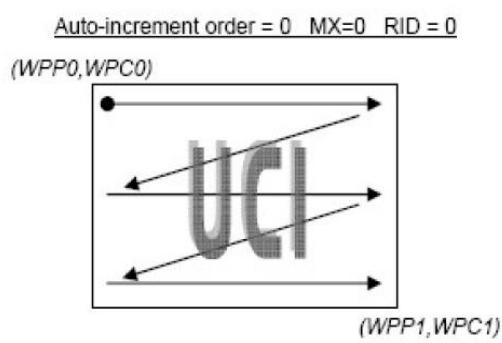

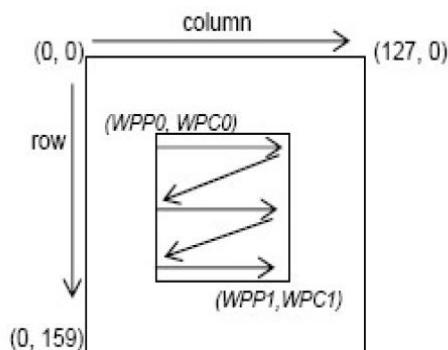

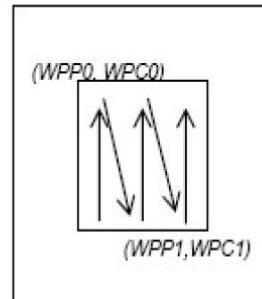

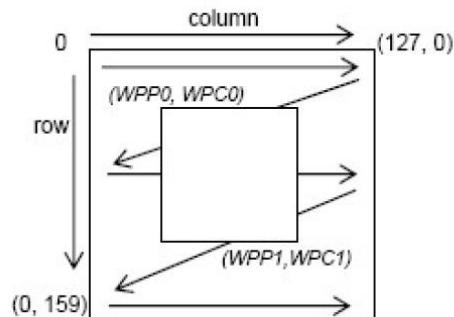

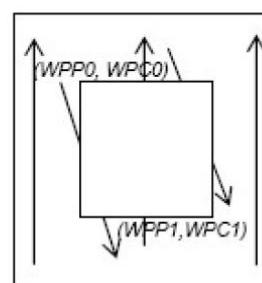

| WPC0             | 7    | 00H     | Window program starting column address. Value range: 0 ~127.                                                                                                                                                                                                           |

| WPP0             | 8    | 00H     | Window program starting row address. Value range: 0~159.                                                                                                                                                                                                               |

| WPC1             | 7    | 7FH     | Window program ending column address. Value range: 0~127.                                                                                                                                                                                                              |

| WPP1             | 8    | 9FH     | Window program ending row address. Value range: 0~159                                                                                                                                                                                                                  |

| MTPC             | 5    | 10H     | MTP Programming Control:<br>MTPC[2:0] : MTP command<br>000 : Idle 001 : Read<br>010 : Erase 011 : Program<br>1xx : For UltraChip's debug use only<br>MTPC[3] : MTP Enable (automatically cleared after each MTP command)<br>MTPC[4] : Ignore/Use MTP. 0: Ignore 1: Use |

| MTP              | 7    | --      | Multiple-Time Programming. For V <sub>LCD</sub> fine tune.                                                                                                                                                                                                             |

| MTPID            | 2    | --      | Multiple-Time Programming. For LCM manufacturer's configuration.                                                                                                                                                                                                       |

| MTPM             | 7    | 00H     | MTP Write Mask. Bit =1: program, Bit=0: no action.                                                                                                                                                                                                                     |

| MTPM1            | 2    | 0H      | MTP Write Mask. Bit =1: program, Bit=0: no action.                                                                                                                                                                                                                     |

| APC              |      | N/A     | Advanced Program Control. For UltraChip only. Please do not use.                                                                                                                                                                                                       |

| Status Registers |      |         |                                                                                                                                                                                                                                                                        |

| OM               | 2    | -       | Operating Modes (Read only)<br>00b: Reset 01b: (Not used)<br>10b: Sleep 11b: Normal                                                                                                                                                                                    |

| MD               | 1    | -       | MTP option flag: 1 for MTP version, 0 for non-MTP version.                                                                                                                                                                                                             |

| MS               | 1    | -       | MTP programming in-progress                                                                                                                                                                                                                                            |

| WS               | 1    | -       | MTP Operation Succeeded                                                                                                                                                                                                                                                |

| ID               | 2    | PIN     | Access the connected status of ID pins.                                                                                                                                                                                                                                |

## 7-2 指令表

### COMMAND TABLE

The following is a list of host commands supported by UC1698u

|      |                  |               |

|------|------------------|---------------|

| C/D: | 0: Control,      | 1: Data       |

| W/R: | 0: Write Cycle,  | 1: Read Cycle |

| #:   | Useful Data bits | -: Don't Care |

|    | Command                                                  | C/D | W/R | D7  | D6                | D5 | D4 | D3       | D2 | D1       | D0 | Action                                         | Default   |

|----|----------------------------------------------------------|-----|-----|-----|-------------------|----|----|----------|----|----------|----|------------------------------------------------|-----------|

| 1  | Write Data Byte                                          | 1   | 0   | #   | #                 | #  | #  | #        | #  | #        | #  | Write 1 byte                                   | N/A       |

| 2  | Read Data Byte                                           | 1   | 1   | #   | #                 | #  | #  | #        | #  | #        | #  | Read 1 byte                                    | N/A       |

| 3  | Get Status & PM                                          | 0   | 1   | GE  | MK                | MY | WA | DE       | WS | MD       | MS | Get {Status, Ver, PMO, Product Code, PID, MID} | N/A       |

|    |                                                          |     |     | Ver | PMO[6:0]          |    |    |          |    |          |    |                                                |           |

|    |                                                          |     |     |     | Product Code (8h) |    |    | PID[1:0] |    | MID[1:0] |    |                                                |           |

| 4  | Set Column Address LSB                                   | 0   | 0   | 0   | 0                 | 0  | 0  | #        | #  | #        | #  | Set CA[3:0]                                    | 0         |

| 5  | Set Column Address MSB                                   | 0   | 0   | 0   | 0                 | 0  | 1  | 0        | #  | #        | #  | Set CA[6:4]                                    | 0         |

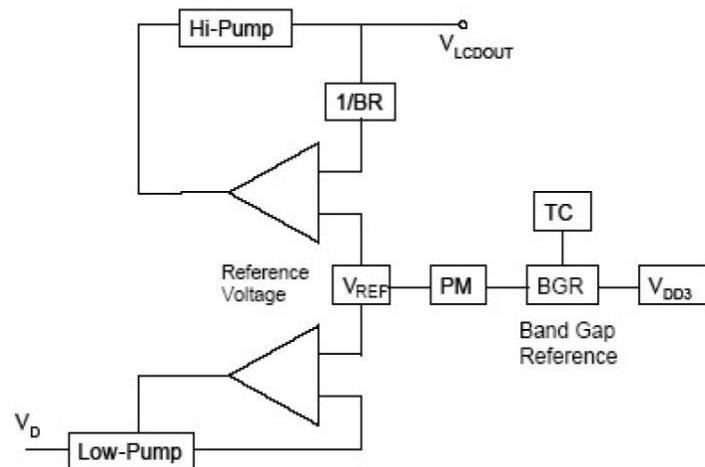

| 6  | Set Temp. Compensation                                   | 0   | 0   | 0   | 0                 | 1  | 0  | 0        | 1  | #        | #  | Set TC[1:0]                                    | 0         |

| 7  | Set Power Control                                        | 0   | 0   | 0   | 0                 | 1  | 0  | 1        | 0  | #        | #  | Set PC[1:0]                                    | 10b       |

| 8  | Set Adv. Program Control (double-byte command)           | 0   | 0   | 0   | 0                 | 1  | 1  | 0        | 0  | 0        | R  | Set APC[R][7:0], R = 0 or 1                    | N/A       |

| 9  | Set Scroll Line LSB                                      | 0   | 0   | 0   | 1                 | 0  | 0  | #        | #  | #        | #  | Set SL[3:0]                                    | 0         |

| 10 | Set Scroll Line MSB                                      | 0   | 0   | 0   | 1                 | 0  | 1  | #        | #  | #        | #  | Set SL[7:4]                                    | 0         |

| 11 | Set Row Address LSB                                      | 0   | 0   | 0   | 1                 | 1  | 0  | #        | #  | #        | #  | Set RA[3:0]                                    | 0         |

| 12 | Set Row Address MSB                                      | 0   | 0   | 0   | 1                 | 1  | 1  | #        | #  | #        | #  | Set RA[7:4]                                    | 0         |

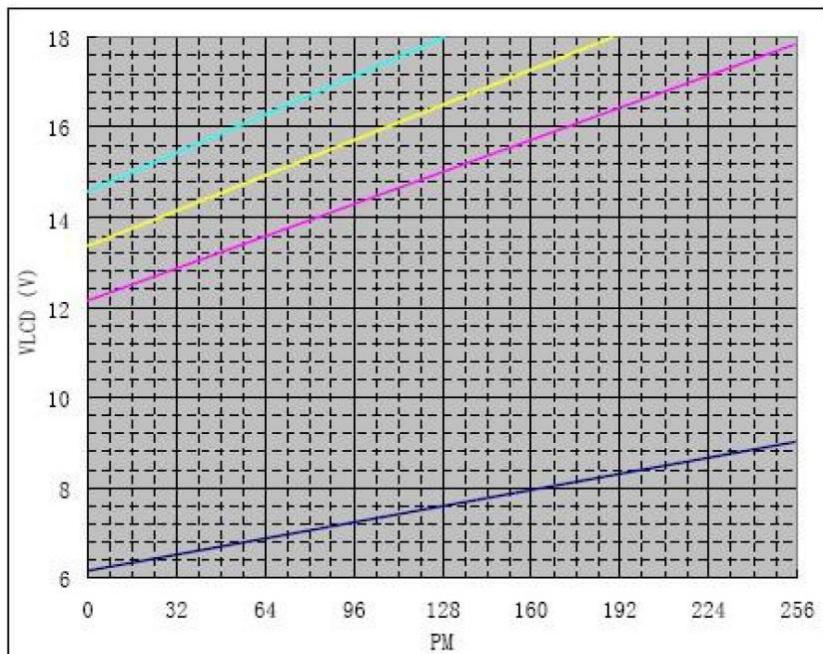

| 13 | Set V <sub>bus</sub> Potentiometer (double-byte command) | 0   | 0   | 1   | 0                 | 0  | 0  | 1        | 0  | 0        | 0  | Set PM[7:0]                                    | 40H       |

| 14 | Set Partial Display Control                              | 0   | 0   | #   | #                 | #  | #  | #        | #  | #        | #  | Set LC[8]                                      | 0         |

| 15 | Set RAM Address Control                                  | 0   | 0   | 1   | 0                 | 0  | 0  | 0        | 1  | 0        | #  | Set AC[2:0]                                    | 001b      |

| 16 | Set Fixed Lines                                          | 0   | 0   | 1   | 0                 | 0  | 1  | 0        | 0  | 0        | 0  | Set {FLT, FLB}                                 | 0         |

| 17 | Set Line Rate                                            | 0   | 0   | 1   | 0                 | 1  | 0  | 0        | 0  | #        | #  | Set LC[4:3]                                    | 10b       |

| 18 | Set All-Pixel-ON                                         | 0   | 0   | 1   | 0                 | 1  | 0  | 0        | 1  | 0        | #  | Set DC[1]                                      | 0         |

| 19 | Set Inverse Display                                      | 0   | 0   | 1   | 0                 | 1  | 0  | 0        | 1  | 1        | #  | Set DC[0]                                      | 0         |

| 20 | Set Display Enable                                       | 0   | 0   | 1   | 0                 | 1  | 0  | 1        | #  | #        | #  | Set DC[4:2]                                    | 110b      |

| 21 | Set LCD Mapping Control                                  | 0   | 0   | 1   | 1                 | 0  | 0  | 0        | #  | #        | #  | Set LC[2:0]                                    | 0         |

| 22 | Set N-Line Inversion                                     | 0   | 0   | 1   | 1                 | 0  | 0  | 1        | 0  | 0        | 0  | Set NIV[4:0]                                   | 1DH       |

| 23 | Set Color Pattern                                        | 0   | 0   | 1   | 1                 | 0  | 1  | 0        | 0  | 0        | #  | Set LC[5]                                      | 0 (BGR)   |

| 24 | Set Color Mode                                           | 0   | 0   | 1   | 1                 | 0  | 1  | 0        | 1  | #        | #  | Set LC[7:6]                                    | 10b       |

| 25 | Set COM Scan Function                                    | 0   | 0   | 1   | 1                 | 0  | 1  | 1        | #  | #        | #  | Set CSF[2:0]                                   | 000b      |

| 26 | System Reset                                             | 0   | 0   | 1   | 1                 | 1  | 0  | 0        | 0  | 1        | 0  | System Reset                                   | N/A       |

| 27 | NOP                                                      | 0   | 0   | 1   | 1                 | 1  | 0  | 0        | 0  | 1        | 1  | No operation                                   | N/A       |